par , 05/08/2022 à 20h24 (3582 Affichages)

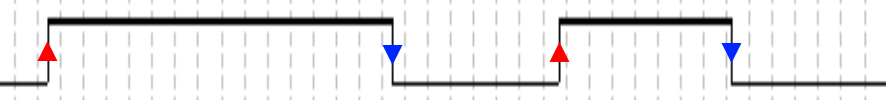

Dans un signal logique, un front est le passage dun état logique à un autre état logique.

On distingue :

- le front montant, qui est le passage de létat bas du signal à létat haut ;

- le front descendant, qui est le passage de létat haut du signal à létat bas.

Fronts montants (flèches rouges), fronts descendants (flèches bleues)

Fronts montants (flèches rouges), fronts descendants (flèches bleues)

Ces fronts sont très utilisés en logique séquentielle. Si on prend le cas particulier dun signal dhorloge (clock) qui sert à synchroniser les circuits numériques, les évolutions du système sont déclenchées sur front de lhorloge (front montant en général).

Ce billet décrit ici un circuit logique dune solution de détection de front (montant ou descendant) sur une carte de développement FPGA, au travers de sa description avec un langage HDL (ici, Verilog, parce que je n'en connais pas d'autres).

Lobjectif est résumé dans les chronogrammes ci-dessous :

Le signal dentrée (in) est un signal logique asynchrone, cest-à-dire dont les fronts peuvent se présenter à nimporte quel moment, sans lien avec le signal dhorloge (clk). Le signal dentrée (in) de la simulation montre 6 fronts, entourés en rouge, quil sagit de détecter.

La détection est marquée dune impulsion sur un cycle dhorloge, repérée en jaune sur le signal de sortie (out). La sortie (out) est synchronisée sur front montant de lhorloge (clk), doù le petit décalage temporel entre le front et limpulsion. La solution synchronisée sera dautant plus pertinente et précise si la fréquence de lhorloge (clk) est grande devant la fréquence du signal dentrée (in).

La solution envisagée passe par lutilisation en cascade de deux bascules de type D (repérées a et b sur le schéma ci-dessous) :

« La bascule D (pour Data) est une bascule comportant uniquement une entrée de données : D. La valeur de l'entrée est recopiée sur la sortie à chaque front d'horloge. », daprès Wikipédia.

Regardons les chronogrammes des sorties des deux bascules lorsquun front se présente sur le signal dentrée in (flèche bleue) :

La première bascule (a) ne sert quà synchroniser le signal dentrée (in) avec lhorloge (clk). À sa sortie, le front montant du signal dentrée (in) est recopié en le décalant au 1er front montant rencontré de lhorloge (1re flèche rouge). En cascadant une deuxième bascule (b), on décale à nouveau le signal issu de la bascule (a) au front montant suivant de lhorloge (la 2e flèche rouge).

Le signal (b) est donc une image « retardée » du signal (a), ce qui permet de comparer à un instant précis un état présent (où le signal dentrée in est maintenant à létat haut) avec un état précédent (où le signal dentrée in était encore à létat bas).

En effet, entre les deux fronts montants dhorloge (flèches rouges), le signal a est à létat haut alors que le signal retardé du cycle précédent b est à létat bas, ce qui indique la présence dun front montant. Pour la détection dun front montant, léquation logique de la sortie out peut alors sécrire :

Comme il faut aussi détecter les fronts descendants, léquation logique de la sortie out doit être complétée et devient :

Vous pouvez vérifier en écrivant les tables de vérité :

doù la présence de la porte XOR (OU exclusif)  du circuit logique.

du circuit logique.

Si en programmation traditionnelle, les lignes du programme mèneront après compilation à des suites dinstructions exécutées séquentiellement par un microprocesseur, il sagit ici de décrire textuellement des comportements qui synthétiseront le circuit logique voulu à la « compilation » du projet.

Le code Verilog qui amène à synthétiser ce circuit est finalement très court, presque intuitif à lécriture (cest le but dun langage HDL haut niveau), mais rempli de chausse-trapes si on raisonne comme en programmation traditionnelle :

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

| module edgeDetector (clk, in, out);

input clk, in;

output out;

reg a, b; // registres internes

assign out = a ^ b; // ^ : symbole du OU exclusif

always @(posedge clk) begin // processus sur front montant de lhorloge

a <= in;

b <= a;

end

endmodule |

- a et b : des « registres » (reg) en Verilog, une entité qui sapproche du concept de variable en programmation traditionnelle, et qui inféreront des bascules D de logique séquentielle à la synthèse (puisque quune bascule D « mémorise » un état à des instants précis).

- assign: assignation en continu, toute modification dans les registres a ou b est continuellement répercutée sur la sortie out.

- Bloc always : processus évalué sur front montant (positive edge) de lhorloge.

Parmi les chausse-trapes du langage Verilog, vous aurez à vous confronter au signe <= qui désigne une affectation « non bloquante », à distinguer de laffectation « bloquante » avec le signe =.

Les guidelines du langage Verilog racontent quil faut utiliser des affectations non bloquantes dans les blocs always qui gèrent de la logique séquentielle (et donc des affectations bloquantes pour gérer de la logique combinatoire). Tenez-vous en à ces recommandations si vous débutez, car en expliquer la raison est une tout autre histoire que je ne raconterai pas ici, mais vous pouvez consulter le document à télécharger http://www.sunburst-design.com/paper...2000SJ_NBA.pdf.

Tous les chronogrammes et les schémas de ce billet ont été obtenus par simulation du module Verilog donné plus haut.

À suivre pour un nouveau circuit logique

du circuit logique.

![Envoyer le billet « [FPGA] Créer un circuit logique pour détecter les fronts dun signal » dans le blog Viadeo](https://forum.developpez.be/images/misc/bookmarksite_viadeo.gif)

![Envoyer le billet « [FPGA] Créer un circuit logique pour détecter les fronts dun signal » dans le blog Twitter](https://forum.developpez.be/images/misc/bookmarksite_twitter.png)

![Envoyer le billet « [FPGA] Créer un circuit logique pour détecter les fronts dun signal » dans le blog Google](https://forum.developpez.be/images/misc/bookmarksite_google.gif)

![Envoyer le billet « [FPGA] Créer un circuit logique pour détecter les fronts dun signal » dans le blog Facebook](https://forum.developpez.be/images/misc/bookmarksite_facebook.gif)

![Envoyer le billet « [FPGA] Créer un circuit logique pour détecter les fronts dun signal » dans le blog Digg](https://forum.developpez.be/images/misc/bookmarksite_digg.gif)

![Envoyer le billet « [FPGA] Créer un circuit logique pour détecter les fronts dun signal » dans le blog Delicious](https://forum.developpez.be/images/misc/bookmarksite_delicious.gif)

![Envoyer le billet « [FPGA] Créer un circuit logique pour détecter les fronts dun signal » dans le blog MySpace](https://forum.developpez.be/images/misc/bookmarksite_myspace.gif)

![Envoyer le billet « [FPGA] Créer un circuit logique pour détecter les fronts dun signal » dans le blog Yahoo](https://forum.developpez.be/images/misc/bookmarksite_yahoo.gif)