SiFive lance ses puces RISC-V de la série Core IP 7 pour lIoT, lembarqué

Et les applications en temps réel, avec des modèles supportant Linux

SiFive est un « fondeur fabless » (qui fait de la conception, mais pas de fabrication) américain basé à San Francisco qui conçoit des puces pour lindustrie des semi-conducteurs et propose des SoC pour microcontrôleurs, lembarqué, lIoT et les applications portables, ainsi quun ensemble doutils pour fournir des capacités de débogage.

Les puces conçues par SiFive sont basées sur larchitecture de jeu dinstructions (ISA) RISC-V, un ISA 64 bits RISC ouvert et libre qui implémente le support dun type particulier de matériel (FPGA, ASIC ) ou un jeu dinstructions RISC sans microcode, ni surcouche darchitecture du type exécution dans le désordre ou dans lordre. Les puces RISC-V open source sont hautement personnalisables contrairement à aux puces ARM et x86.

La société a récemment annoncé la disponibilité de ses nouvelles puces RISC-V appartenant à la série Core IP 7 de SiFive. Elles sont divisées en trois familles E7, S7 et U7.

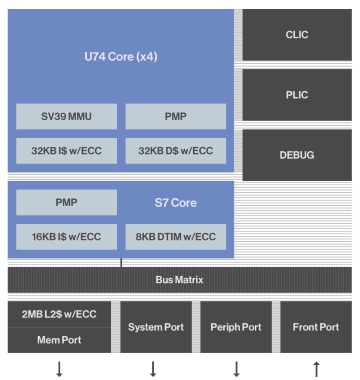

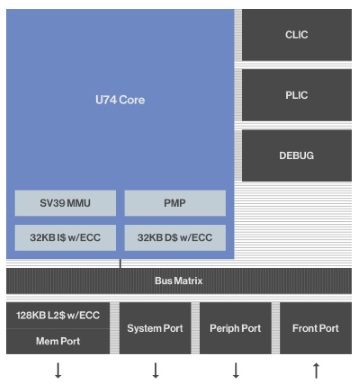

Les puces Core IP de la famille E7 offrent une architecture hétérogène et personnalisable avec des capacités en temps réel. Celles de la famille S7 sont caractérisées par une architecture 64 bits haute performance ciblant en particulier le marché de lembarqué. Les SoCs Core IP de la famille U7, quant à eux, sont capables de faire tourner des applications Linux et caractérisés par une architecture mémoire hautement configurable pour la personnalisation spécifique au domaine.

La famille E7 Core IP comprend notamment les puces 32 bits E76 et E76-MC ainsi que les puces 64 bits S76 et S76-MC. Les puces 64 bits U74 (2,5 DMIPS, mono cur avec 128 KB de cache L2) et U74-MC (2,5 DMIPS, quad-cur avec 2 MB de cache L2) sont semblables au Cortex-A55 d'ARM et, comme toutes les autres puces de la famille U7, elles prennent entièrement en charge Linux.

Ces nouvelles puces ont été optimisées afin dêtre plus performantes et moins énergivores. Daprès SiFive, elles devraient être capables de prendre en charge les appareils de faible puissance les plus avancés ainsi que le déchargement intelligent des charges de travail au niveau des Datacenter. Ces nouvelles puces RISC-V devraient apporter ou optimiser le support de la 5G, du Big Data, de la réalité augmentée, de la réalité virtuelle, de la localisation et la cartographie simultanées (SLAM)... sur les équipements de la prochaine génération.

Les puces de la série SiFive 7 offre des capacités de traitement évolutives avec 8+1 curs par clusteur et ladressabilité mémoire en 64 bits. Elles bénéficieraient, en outre, doptimisations pour augmenter leur niveau de tolérance aux pannes et se prémunir contre certaines attaques par canal latéral.

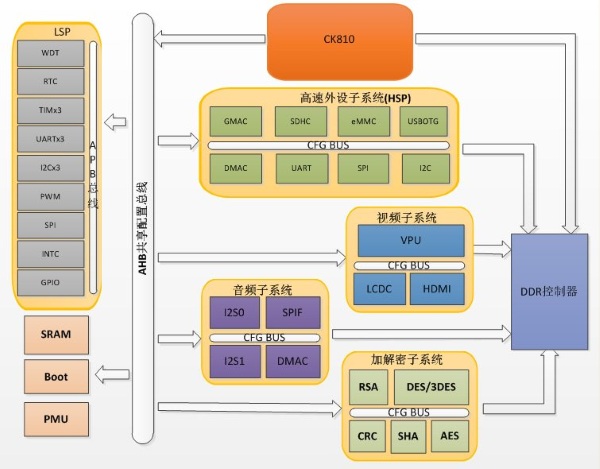

Signalons au passage qu'une architecture C-SKY dérivée de RISC-V développée par la société chinoise Hangzhou C-SKY Microsystems sera supportée par le noyau Linux 4.20 (ou 5.0 selon la nouvelle nomenclature). Apparemment, C-SKY diffère suffisamment de RISC-V pour être supportée séparément par le noyau Linux. La conception initiale du C-SKY CK810 semble le destiner aux appareils Linux bas de gamme.

Source : RISCV, Linux Gizmos

Et vous ?

Quen pensez-vous ?

Voir aussi

SiFive va lancer une carte de développement RISC-V supportée par Linux, HiFive Unleashed est attendue dès le mois de mars

Les processeurs open source RISC-V reçoivent le soutien de 80 entreprises technologiques parmi lesquelles Samsung, Google, Nvidia et même WD

SiFive lance un processeur RISC-V supporté par Linux, Unix et FreeBSD, une menace pour les architectures propriétaires comme ARM ?

La Fondation RISC-V annonce la création d'un comité permanent de sécurité dont l'objectif est de développer un consensus sur les meilleures pratiques

Répondre avec citation

Répondre avec citation

Partager